# Building and Testing a Photolithography System

Kyel Lambert and Dr. M. S. Crosser Physics Department, Linfield College

#### Abstract

Photolithography is a technique used to deposit metals onto substrates in specific patterns. The process uses light to transfer geometric patterns onto a light sensitive photoresist on the surface of a substrate. We have built a low-cost, maskless photolithographic system assembled from a computer, a consumer projector, and a microscope. The photoresist is spun in a modified food processor and baked on a standard hot plate. Exposing the photoresist only takes a few minutes and allows for multiple runs on the same substrate in a short amount of time. Through multiple exposures, we can make features ranging from approximately 1 µm to 785 µm, which is especially useful when making contacts using the large features.

## Preparation

To spin coat the silicon chip with photoresist, a modified food processor, candle wax, hot air gun, and hot plate were used

Fig. 1: Photograph of a modified food processor (1) with platform (2), hot plate (3), hot air gun (4) and candle wax (5).

- •Work was done under red lights so as to not expose the photoresist before intended

- Wax was placed on the platform (Fig. 1.2) and melted.

The silicon chip was then attached

- After spinning photoresist, the chip is baked on a hot plate for 3 minutes at 100° C

#### **Process**

The photoresist is most sensitive to light with 436 nm wavelength.

Blue images are used to expose the resist and red images are used for alignment purposes

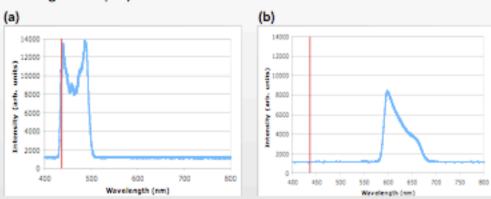

Fig. 2: The red line (436 nm) represents peak sensitivity of the resist. This wavelength lines up along a maximum of intensity for blue light (a) and is far from the maximum of red light (b).

- PowerPoint was used to draw patterns. Identical slides were created with one in red and one in blue

- The projector directs the image off a mirror, through the microscope and onto the chip. The red slide was used for alignment, and the blue slide to expose the resist

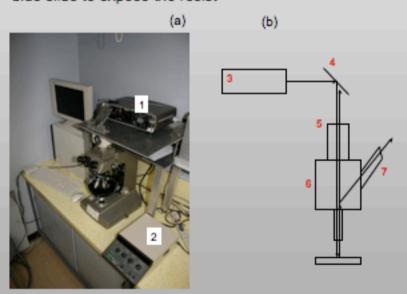

Fig. 3: (a) Photograph of computer, projector (1), microscope and automatic exposure control unit (2). (b) Schematic of the light traveling through the system. Light starts at the projector (3) and is redirected by the mirror (4). It then passes through the shutter (5) of the automatic exposure control unit and then the microscope (6). After reflecting off the sample, the image can be observed through the viewing lens (7).

Metal is then deposited onto the chip using thermal evaporation

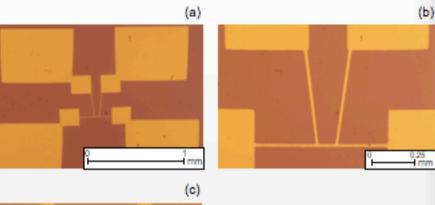

The chips are cleaned in acetone to remove remaining resist while leaving metal in the desired pattern. Sample images of the final result are shown in Fig. 4

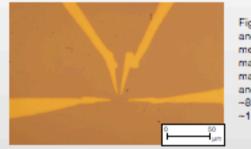

Fig. 4: Gold pattern on a silicon chip at 5x (a) and 20x (b) magnification. A test pattern for measuring resistivity is shown in (c) at 50x magnification. The large rectangles in (a) were made by doing a second round of exposure and are ~785 µm in width. The lines in (b) are ~8 µm wide and the smallest features in (c) are ~1 µm.

### Results and Conclusions

- We were able to deposit metal in a specific pattern onto silicon chips.

- We developed two techniques for multiple exposures.

- One process exposes the photoresist at 50x magnification, then switches the microscope to 5x magnification to expose connecting patterns.

- The other technique first exposes a pattern and partially develops it. Then the first pattern is used to align and expose larger features (rectangles in Fig. 4a).

- Using the two techniques creates small features with a resolution of ~1 µm while also creating large features.

- The equipment is inexpensive compared to masked lithography and a spin coat machine.

#### **Future Work**

Our goal is to use the large features of the patterns as metal contacts for electrical leads. The pattern in Fig. 4c is designed to connect to a piece of graphene that is on the surface of a silicon chip. Using the metal contacts, we could pass a current through the graphene and also measure the voltage across it. With this in place, we plan to test electrical properties of graphene.

#### Acknowledgements

This project was supported by the Linfield College Faculty/Student Collaborative Research Grant.